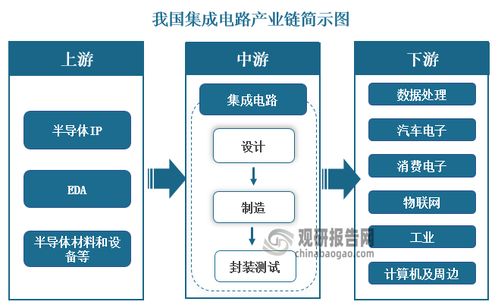

模擬集成電路(Analog IC)設(shè)計(jì)是現(xiàn)代電子系統(tǒng)的核心,它將抽象的電路概念轉(zhuǎn)化為物理硅片上的復(fù)雜結(jié)構(gòu)。這一過程遵循一個(gè)嚴(yán)謹(jǐn)而迭代的設(shè)計(jì)流程,而版圖設(shè)計(jì)則是連接電路原理與物理實(shí)現(xiàn)的關(guān)鍵橋梁。本文將概述模擬集成電路的標(biāo)準(zhǔn)設(shè)計(jì)流程,并深入探討版圖設(shè)計(jì)的基礎(chǔ)知識(shí)。

一、模擬集成電路設(shè)計(jì)流程

模擬集成電路設(shè)計(jì)是一個(gè)自上而下(Top-Down)與自下而上(Bottom-Up)相結(jié)合的系統(tǒng)工程,通常包含以下幾個(gè)主要階段:

- 系統(tǒng)定義與規(guī)格制定:明確芯片的功能、性能指標(biāo)(如增益、帶寬、功耗、噪聲)、工作環(huán)境以及封裝形式。這是所有后續(xù)設(shè)計(jì)的藍(lán)圖。

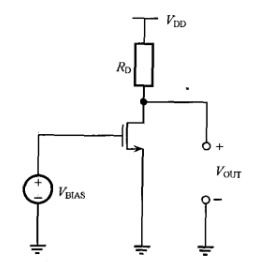

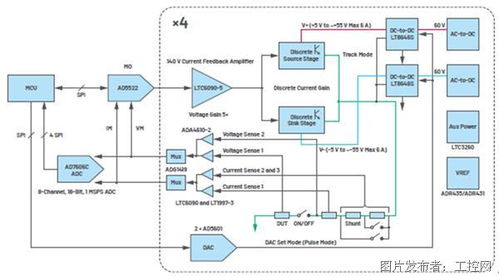

- 架構(gòu)設(shè)計(jì)與電路設(shè)計(jì):根據(jù)規(guī)格,選擇合適的電路架構(gòu)(如運(yùn)算放大器、鎖相環(huán)、數(shù)據(jù)轉(zhuǎn)換器等)。隨后進(jìn)行晶體管級(jí)的電路設(shè)計(jì),使用SPICE等仿真工具驗(yàn)證電路的直流、交流、瞬態(tài)等特性,確保其滿足理論性能要求。

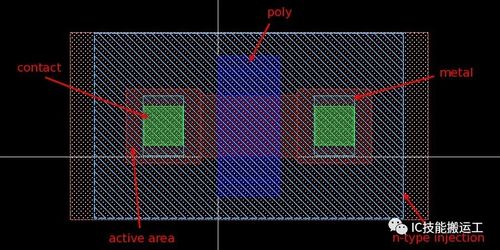

- 版圖設(shè)計(jì):將經(jīng)過驗(yàn)證的電路原理圖轉(zhuǎn)化為一系列幾何圖形(版圖),這些圖形定義了制造過程中各層材料(如多晶硅、金屬、擴(kuò)散區(qū))的形狀、尺寸和相對(duì)位置。這是物理實(shí)現(xiàn)的第一步,其質(zhì)量直接決定芯片的性能、可靠性和制造成本。

- 物理驗(yàn)證:對(duì)生成的版圖進(jìn)行嚴(yán)格的檢查,主要包括:

- 設(shè)計(jì)規(guī)則檢查(DRC):確保版圖符合芯片制造廠(Foundry)的工藝加工極限規(guī)則,如最小線寬、最小間距等。

- 電路圖與版圖一致性檢查(LVS):確認(rèn)版圖所代表的電路連接關(guān)系與原始電路原理圖完全一致,避免連接錯(cuò)誤。

- 寄生參數(shù)提取(PEX):從版圖中提取導(dǎo)線電阻、寄生電容等非理想寄生參數(shù),生成包含這些寄生效應(yīng)的新網(wǎng)表。

- 后仿真:將提取出的寄生參數(shù)反標(biāo)回電路仿真模型,進(jìn)行帶寄生效應(yīng)的電路仿真。這是評(píng)估版圖對(duì)電路性能(如速度、功耗、噪聲)影響的關(guān)鍵步驟,通常需要根據(jù)結(jié)果反復(fù)優(yōu)化版圖。

- 流片與測(cè)試:將所有最終確認(rèn)的版圖數(shù)據(jù)(通常為GDSII格式)提交給芯片制造廠進(jìn)行生產(chǎn)(即“流片”)。芯片制造完成后,在測(cè)試臺(tái)上對(duì)樣片進(jìn)行全面的功能和性能測(cè)試,驗(yàn)證其是否達(dá)到設(shè)計(jì)規(guī)格。

二、版圖設(shè)計(jì)基礎(chǔ)

版圖設(shè)計(jì)是藝術(shù)與技術(shù)的結(jié)合,其核心目標(biāo)是在滿足所有物理和電氣約束的前提下,實(shí)現(xiàn)最優(yōu)的性能、面積和可靠性。以下是幾個(gè)基礎(chǔ)而關(guān)鍵的概念:

- 工藝層與設(shè)計(jì)規(guī)則:芯片制造工藝定義了多種材料層(如N阱、有源區(qū)、多晶硅、金屬層、接觸孔、通孔)。每一層都有嚴(yán)格的設(shè)計(jì)規(guī)則,版圖設(shè)計(jì)必須絕對(duì)遵守這些規(guī)則,否則會(huì)導(dǎo)致制造失敗或性能缺陷。

- 匹配性設(shè)計(jì):對(duì)于差分對(duì)、電流鏡等對(duì)器件對(duì)稱性要求極高的電路,版圖必須采用精密匹配的布局技巧,如共質(zhì)心結(jié)構(gòu)、交叉耦合、添加虛擬器件等,以抵消工藝梯度帶來的失配,確保電路精度。

- 噪聲隔離與抑制:模擬電路對(duì)噪聲(特別是襯底噪聲和電源噪聲)極為敏感。版圖設(shè)計(jì)中需采用保護(hù)環(huán)、隔離阱、獨(dú)立的電源/地線、合理的布線策略(如信號(hào)線與噪聲線隔離、采用屏蔽線)等手段來最小化噪聲干擾。

- 寄生效應(yīng)控制:寄生電阻和電容會(huì)降低電路速度、增加功耗、引起信號(hào)串?dāng)_。通過使用更寬的導(dǎo)線(減小電阻)、增大敏感節(jié)點(diǎn)間距(減小耦合電容)、優(yōu)化布線走向等方法,可以有效地控制寄生效應(yīng)。

- 可靠性考慮:包括電遷移(大電流導(dǎo)線需足夠?qū)挘⑻炀€效應(yīng)(防止工藝中電荷積累損壞柵氧)、閂鎖效應(yīng)(通過合理的阱和襯底接觸布局來預(yù)防)等。

- 面積優(yōu)化:在滿足性能和可靠性要求的基礎(chǔ)上,緊湊的布局可以降低芯片成本。這需要對(duì)器件布局、布線通道進(jìn)行精心規(guī)劃。

結(jié)論

模擬集成電路的設(shè)計(jì)流程是一個(gè)環(huán)環(huán)相扣、反復(fù)迭代的精密過程。其中,版圖設(shè)計(jì)絕非簡(jiǎn)單的“畫圖”,而是將電路性能、制造工藝和物理現(xiàn)實(shí)深度融合的創(chuàng)造性工作。扎實(shí)的版圖設(shè)計(jì)基礎(chǔ)——深刻理解工藝規(guī)則、匹配原理、寄生效應(yīng)和噪聲機(jī)制——是設(shè)計(jì)出高性能、高可靠性模擬芯片的基石。隨著工藝節(jié)點(diǎn)的不斷進(jìn)步,版圖設(shè)計(jì)面臨的挑戰(zhàn)也日益增加,其重要性在集成電路設(shè)計(jì)領(lǐng)域中愈發(fā)凸顯。